## DESIGN NOTES

## LTC1735 Provides Low Cost, Efficient Mobile CPU Power

Design Note 199

Randy G. Flatness

The LTC®1735 is the newest member of Linear Technology's third generation of synchronous step-down controllers. This controller uses the same constant frequency, current mode architecture and Burst Mode™ operation as the industry standard LTC1435/LTC1437 controllers but with improved features. With OPTI-LOOP™ compensation, new protection circuitry, tighter load regulation and stronger MOSFET drivers, the LTC1735 is ideal for the current and future generations of mobile CPUs. A companion part, the LTC1736, has all the features of the LTC1735 plus 5-bit VID voltage programming according to Intel mobile processor specifications.

The LTC1735 is pin compatible with the previous generation LTC1435/LTC1435A controllers with only minor external component value changes. New protection features include internal foldback current limiting, output overvoltage crowbar and optional short-circuit shutdown. The 0.8V reference supports the low output voltages and 1% accuracy that will be demanded by future microprocessors. A constant operating frequency (synchronizable up to 500kHz) is set by an external capacitor,  $C_{\rm OSC}$ , allowing maximum flexibility in optimizing efficiency.

The LTC1735's OPTI-LOOP compensation removes the constraints placed on  $C_{OUT}$  by other controllers (such as restrictions on very low ESR) for proper operation. A maximum duty cycle limit of 99% provides low dropout operation, which extends operating time in battery-operated systems. A wide input supply range allows operation from 3.5V to 30V (36V maximum).

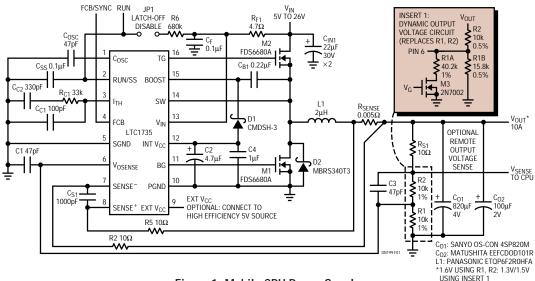

## Low Cost Dynamic VID for Pentium® III Processors

The circuit in Figure 1 generates CPU power (1.6V at 10A) from input voltages of 5V to 26V. Adding the low cost components shown in the insert of Figure 1 creates a dynamic VID two-level output voltage. This implementation produces output voltages of 1.3V with  $V_{G}$  low and 1.5V with  $V_{G}$  high. The LTC1735 has overvoltage protection that tracks the programmed output voltage, always protecting the CPU. If a power good output is needed, the LTC1735 can be replaced with the increased functionality LTC1735-1.

▲7, LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode and OPTI-LOOP are trademarks of Linear Technology Corporation. Pentium is a registered trademark of Intel Corporation.

The RUN/SS capacitor,  $C_{SS}$ , (refer to Figure 1) is used initially to turn on and limit the inrush current of the controller and as a short-circuit timer. If the output voltage falls to less than 70% of its nominal output voltage after  $C_{SS}$  is charged, it is assumed that the output is in a severe overcurrent and/or short-circuit condition and  $C_{SS}$  begins discharging. If the condition lasts for a long enough period, as determined by the size of  $C_{SS}$ , the controller will be shut down until the RUN/SS pin voltage is recycled. Jumper JP1 disables the overcurrent latch-off.

New internal protection features in the LTC1735 controller include foldback current limiting, short-circuit detection, short-circuit latch-off and overvoltage protection. These features protect the PC board, the MOSFETs and the CPU against faults.

Why should you defeat overcurrent latch-off? During the prototyping stage of a design, there may be a problem with noise pickup or poor layout causing the protection circuit to latch off. Defeating this feature will allow easy troubleshooting of the circuit and PC layout. The internal short-circuit detection and foldback current limiting remain active, thereby protecting the power supply system from failure. After the design is complete, you can decide whether to enable the latch-off feature.

The LTC1735 current comparator allows a maximum MOSFET current of 75mV/R<sub>SENSE</sub>. The use of a low loss sense resistor not only provides accurate current limiting, but allows the use of arbitrarily low output capacitor ESR values for outstanding load-step response. A  $0.005\Omega$  sense resistor programs a maximum load current of 10A, (higher currents may be set by lowering R<sub>SENSE</sub>). The LTC1735 includes current foldback to help further limit load current when the output is shorted to ground. If the output falls by more than one-half, the maximum sense voltage is decreased to limit dissipation in the bottom MOSFET, resulting in a short-circuit current of 3.5A. Note that this function is always active and is independent of the short-circuit latch-off.

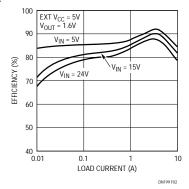

Figure 2. Efficiency for Figure 1

The FCB pin is a multifunction pin that controls the operation of the synchronous MOSFET, is an input for external clock synchronization and reduces noise and RF interference by disabling Burst Mode operation. When the FCB pin drops below its 0.8V threshold (FCB = 0V), continuous mode operation is forced. In this case, the top and bottom MOSFETs continue to be driven synchronously regardless of the load on the main output.

The operating frequency is set to 270kHz by  $C_{OSC}$ . The LTC1735's internal oscillator can be synchronized to an external oscillator by applying a clock signal of at least  $1.5V_{P-P}$  to the FCB pin. When synchronized to an external frequency, Burst Mode operation is disabled but cycle skipping occurs at low load currents because current reversal is inhibited. The bottom gate will come on every 10 clock cycles to ensure that the bootstrap capacitor is kept refreshed and to keep the frequency above the audio range. The rising edge of an external clock applied to the FCB pin starts a new cycle. The range of synchronization with  $C_{OSC} = 47pF$  is from 240kHz to 400kHz.

The LTC1735 uses a new "soft latch" OVP circuit. Regardless of the operating mode, the synchronous MOSFET is forced on whenever the output voltage exceeds the regulation point by more than 7.5%. However, if the voltage then returns to a safe level, normal operation is allowed to resume, thereby preventing latch-off caused by noise or voltage reprogramming. This is important when dynamically changing output voltage since the overvoltage protection threshold tracks the new output voltage, always protecting the CPU.

Previous latching crowbar schemes for overvoltage protection have a number of problems. One of the most obvious, not to mention most annoying, is nuisance trips caused by noise or transients momentarily exceeding the OVP threshold. Each time that this occurs with latching OVP, a manual reset is required to restart the regulator.

The LTC1735 is designed to be used in higher current applications than the LTC1435 family. Stronger gate drives allow paralleling multiple MOSFETs or operating at higher frequencies. The LTC1735 has been optimized for low output voltage operation by reducing the minimum ontime to less than 200ns. Remember though, transition losses can still impose significant efficiency penalties at high input voltages and high frequencies. Just because the LTC1735 can operate at frequencies above 300kHz doesn't mean it should.

For literature on our DC/DC Controllers, call **1-800-4-LINEAR**. For applications help, call (408) 432-1900, Ext. 2593